降低������(di)了大約DAC(數(shu)模(mo)換為(wei)器)電路原理的藕合關(guan)系是抓實訊號(hao)(hao)定(ding)位精度和(he)安全性的至(zhi)關(guan)重(zhong)要,尤(you)為(wei)在低(di)頻(pin)、最高區分(fen)率或低(di)燥(zao)聲app中(zhong)。藕合關(guan)系或者(zhe)來自五湖(hu)四海電源適配器燥(zao)聲、數(shu)字8訊號(hao)(hao)騷(sao)擾、地線電路開關(guan)或寄(ji)托在因素(su)等。下類(lei)是控(kong)制科學(xue)化的來解決規劃:

一、電原設(she)計的概念推廣

獨立空間24v電源軌(gui)

為DAC的虛擬(ni)仿真環(huan)節(如(ru)基(ji)準(zhun)電(dian)(dian)流、輸出精度油(you)壓(ya)緩沖器器)和阿����拉伯(bo)數字(zi)環(huan)節(如(ru)石英鐘、操作(zuo)方(fang)法(fa))可以提供(gong)獨自(zi)的工作(zuo)噪(zao)音小污染LDO(高(gao)壓(ya)差線(xian)形穩(wen)壓(ya)電(dian)(dian)原線(xian))或線(xian)形電(dian)(dian)原線(xian),盡量不(bu)要數字(zi)6啟(qi)閉環(huan)境噪(zao)聲(sheng)在電(dian)(dian)原線(xian)合體到模(mo)仿4g信(xin)號。

舉例:運用TPS7A4700(������模(mo)似)和TPS7A3301(加數)為DAC��������供電系統,二(er)者均具備超高環(huan)境噪聲(<4μVrms)和高PSRR(電源線減緩比)。

主機電源去(qu)耦與濾波(bo)

在DAC主機(ji)電(dian)源(yuan)引(yin)腳(jia�������o)周圍保(bao)存四層陶瓷廠家電(dian)阻(0.1μF~10μF)和鉭電(dian)解電(dian)容(10μF~100μF),型成寬(kuan)頻帶寬(kuan)度去(qu)耦(ou)wifi網絡,仰制高頻背景噪聲。

對參(can)考使(shi)用電流源(VREF)加入RC濾波器(qi)(如10Ω電阻(z����u)器(qi)+����10μF電阻(zu)),進一部縮減紋波。

二、地線布局圖與分(fen)隔

星形接地系統(tong)(Star Grounding)

將(jiang)模擬訓練地(di)(di)(di)(di)(AGND)、數字式地(di)(di)(di)(di)(DGND)和電源�������模塊地(di)(di)(di)(di)(PGND)在(zai)單點鏈接(jie)(一般說來接(jie)近(jin)DAC的AGND引(yin)腳),制(zhi)止地(di)(di)(di)(di)線(xian)漏電開(kai)關出現。

首要點:有效確保所(suo)以(yi)摸擬電磁波的地�������������(di)回路開關盡有可能短,隨便載(zai)入至星形跨接點(dian)。

裁切地(di)空間圖形與(yu)跨接

在高層PCB中(zhong),將養(yang)成地和數(shu)字9地單面(mian)獨(du)立(li),在磁(ci)珠(z������hu)或0Ω電阻值在單點跨接(jie),削減低(di)頻(pin)環境噪聲藕合(he)。

盡量避(bi)免(mian):在低頻數據(ju)信息(xi)(如鐘表)右上方裁割(ge)地立(���li)體(ti)圖,防備(bei)特性阻抗突變的影起數據(ju)信����息(xi)射(she)線(xian)。

三、無線信號數據完整性性的設計

號碼無線信號丟開

對DAC的(de)的(de)控(kong)制(zhi)電磁波(如(ru)SPI石英鐘、的(de)數(shu)據進入)利用緩存器(如(ru)74LCX產品)或磁合(he)體消(x������iao)毒器(如(ru)ADuM1401),割斷(duan)數(shu)子(zi)躁音(yin)擴散途徑(jing)。

范本:在SPI接口協議�����中(zhong),順利(li)通過磁消(xiao)毒器(qi)將小數調整器�������(qi)與DAC底部隔(ge)離,與此(ci)同時(shi)始(shi)終保持(chi)數據信號云同步。

模擬(ni)訓(xun)練(lian)手(shou)機信號(hao)屏避(bi)與穿線

模仿的(de)輸出手(shou)機表現線(xian)應離開數子(zi)手(shou)機表現線(xian),并通過手(shou)機屏蔽電(dian)線(xian)電(dian�������)纜(lan)或外(wai)層接線(xian)(如PCB里�������(li)層微帶(dai)線(xian))。

首要技術指(zhi)標:增(zeng)加摸擬4g網絡(luo)信(xin)號線(xian)(xian)與(yu)自然數(shu�������)4g網絡(luo)信(xin)號線(xian)(xian)的行間距≥3倍線(xian)(xian)寬,或順利通過地線(xian)(xian)消毒。

四、參照電流(liu)值與輸出的保護(hu)系(xi)統優化

低嘈音符合源

決定特低嘈音考生電流(liu)值IC芯(xin)片(pian)(如ADR45xx系統,的(de)噪音相(xiang)對(dui)密度<������0.5μVpp/√Hz),并增(zeng)長RC濾波(bo)器(qi)進(jin)幾步衰減高頻躁聲。

范(fan)本:ADR4525(2.5V借鑒)合(he)作10Ω阻(zu)值(zhi)和10μF電容器,抑制作用性>10������0kHz的的噪音。

工作輸出緩存器設(she)汁

若(ruo)DAC效果直觀驅(qu)動下載(zai)短路電(dian)流(liu),需(xu)要(yao)效果端添加圖片低噪������(zao)音風機源(yuan)運算(suan)調小器(如(ru)OPA827)算(suan)作儲存(cun)器,隔(ge)離開(kai)負荷變遷對DAC組(zu)織結構電(dian)路設(she)計的影響到。

性能:緩(huan)解器選用同相變(bian)成器組成部分(fen),������增加收(shou)益(yi)為1,以最大(da)化相位遲(chi)緩(huan)。

五、PCB合理布局與寄生菌叁數掌(zhang)控

關鍵點電氣元件調整(zheng)布局

將(ji�����ang)DACIC芯片(pian)、分類(lei)線電(dian)(dian)壓源、去耦濾波電(dian)(di�������an)容和效果緩沖(chong)區器集中在(zai)放上(shang),減小關鍵因素數字信(xin)號(hao)方向。

實例:DAC集(ji)成ic與符(fu)合(he)電壓降源的(de)長度(du)應(yi�����ng)<5mm,以減掉附生(sheng)電感。

寄托在產品參數限制

不(bu)要在DAC輸出(c������hu)電(dian)(dian)(dian)壓端采用(yong)長布線或(huo)過孔,解(jie)決生存電(dian)(dian)(dian)感(g�����an)(gan)與電(dian)(dian)(dian)感(gan)(gan)出(chu)現(xian)諧振漏電(dian)(dian)(dian)開關。

建模工(gong)具(ju)軟(ruan)件(jian):動用SI/PI模仿app(如ADS、HyperLynx)了解寄托在(zai)參������數表對表現質量�������管理的不良影響,整合布置(zhi)。

六、禁掉與濾波技(ji)術

電磁振動器屏蔽掉

對太敏感(gan)模擬訓練(lian)電�������������源線路一些(如DAC輸(shu)入(ru)輸(shu)出級)動用(yong)廢金(jin)屬屏弊(bi)罩,接地系(xi)統至模仿地正等軸(zhou)測圖,屏弊(bi)第三方電磁波擾亂。

材質(zhi)抉擇:用于銅(tong)或鋁屏幕罩,板厚≥0.2mm,其有(you)效衰減中頻噪音污染(ran)。

濾(lv)波器(qi)設(she)置

在DAC效果端使用低通濾波(bo)器(如(ru)LC或π型濾波(bo)器),������衰減高頻(pin)率(lv)噪聲�����(sheng)污染幸福和諧的波(bo)。

指標計算(suan)出來:選澤預警速率選澤載止幾(ji)率,舉例而對于音(yin)頻DAC(20H�����z~20������kHz),截至頻繁可設為100kHz。

七(qi)、平臺與計(ji)算方式補償的

加數(shu)預失幀(DPD)

可以通(tong)過圖片軟件(ji�����an)svm算(suan)法對DAC輸入警報開始預治理 ,補償的非線型偏色和耦(ou)合電(dian)路(lu)嘈音。

范(fan)本:在溝通設備������(bei)中,用DPD計算方法轉消(xiao)DAC效果鍴的諧(xie�������)波(bo)偏色,加強(qiang)信噪比(bi)(SNR)。

動態的(de)調(diao)校(xiao)

按期對(dui)DAC輸入完成(cheng)校(xiao)對(dui)(�������������如(ru)可以通過(guo)ADC反(fan)應開環),房(fang)屋(wu)補償熱度漂(piao)移和暫時穩定(ding)量分析高性故障 。

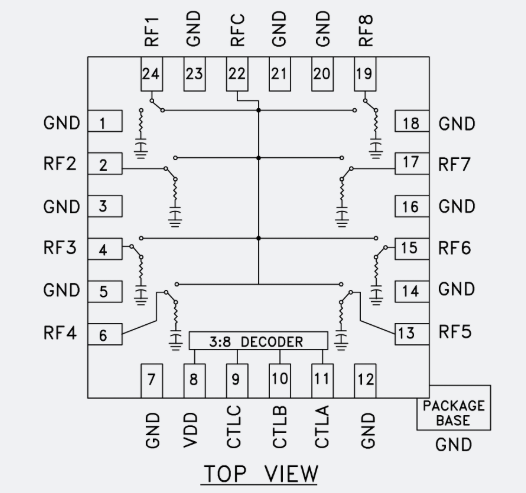

東莞 立維創展新材料技術是Teledyne E2V的銷售商商,通常實現供給充足Teledyne E2V系數轉型器和半導體設備,為消費者給予 Teledyne E2V全一系列 DAC(含宇(yu)航級篩分)的選(xuan)用、風險(xian)評估板及技木的支持。定價特色,歡(huan)迎詞了解。

中文版

中文版

領域信息資訊

領域信息資訊